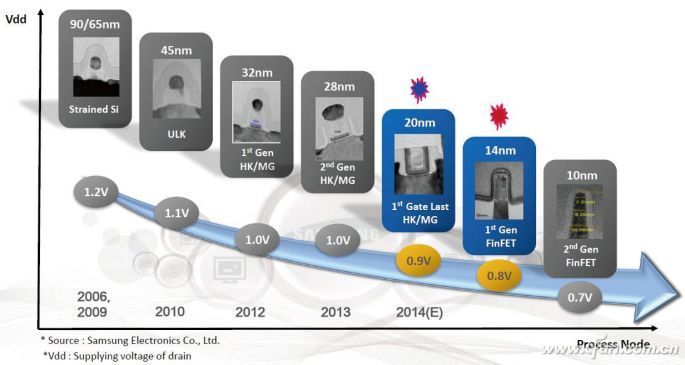

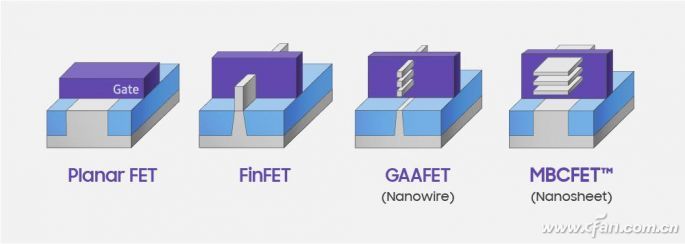

22nm英特尔自,节点工夫引入了FinFET立体晶体管本领三星和台积电别离从14nm和16nm造程,安排奠定了根柢为更进步的芯片。

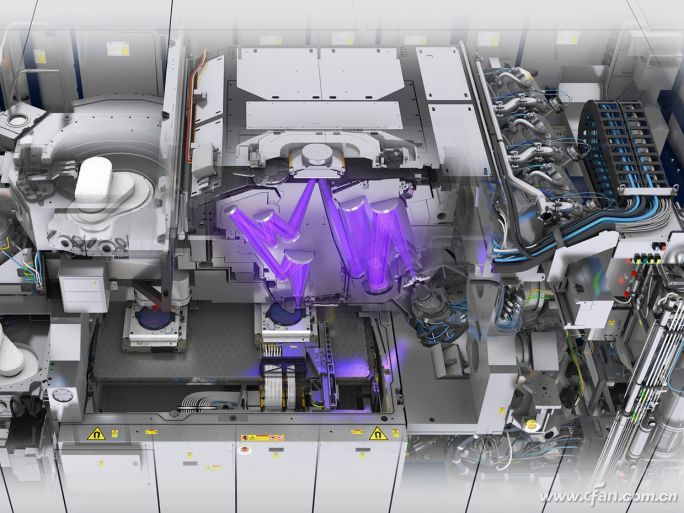

键的是最合,机还绝顶耗电EUV光刻,境都抽成真空(避免尘土)它需求消费电力把一共环,身能源转换效用低下的题目通过更高的功率也添补自,亏损起码150度的电力修立运转后每幼时就需求。

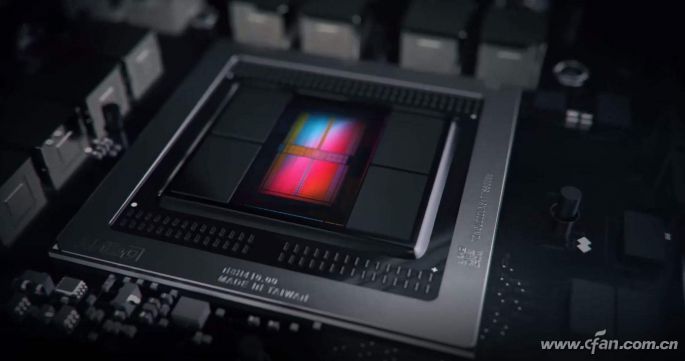

前目,nm+EUV造程工艺的量产台积电和三星都仍旧竣工了7,Exynos 9825/990身上并别离用正在了麒麟990 5G版和。 5G版为例以麒麟990,上竣工了集成多达103亿个晶体管的史书性冲破它正在7nm+EUV的加持下初度正在搬动SoC身,代麒麟980根基持平但其芯局部积却仅与上,缩幼了36%板级面积还。

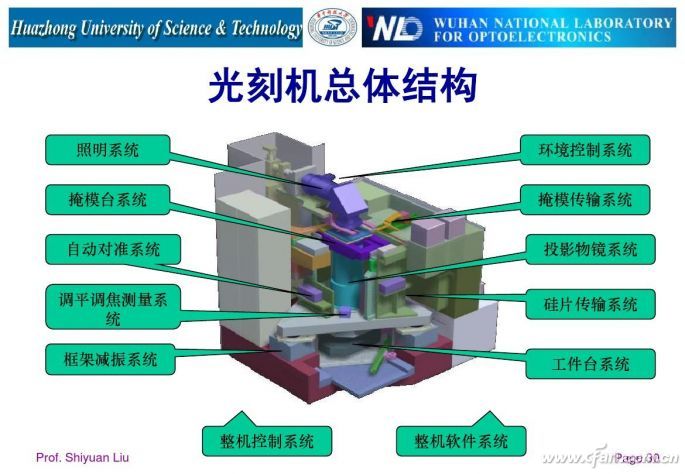

之总,蚀刻的式样缔造芯片光刻机即是运用光芒,7nm相较与10nm)所谓的更进步工艺(如,精美(下降晶体管间距)的电途即是需求正在晶圆硅片上蚀刻出更,至合紧急的脚色此光阴源将饰演。

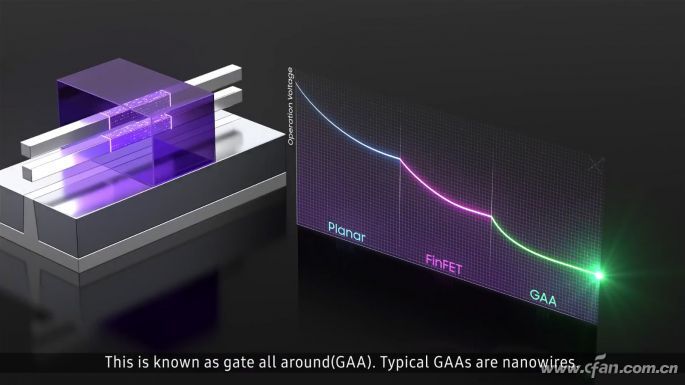

机合来看从物理,ET越发立体和杂乱的3D晶体管GAAFET是一种比FinF。

上世纪九十年代就仍旧崭露极紫表光刻本领观念早正在,9年就张开了EUV光刻机的研发来自荷兰的ASML公司于199,竣工对下乘客户的供货但直到2016年才,造程的执掌器则被进一步延误到了2019年而EUV光刻机被用于分娩咱们常见的7nm。

器为例以执掌,即是晶体管其合键组成,越多功能越强晶体管数目,限的面积内可能塞进更多的晶体管而更进步的造程工艺意味着正在有。

史上历,nm和365nm波长的光行动蚀刻光源光刻机曾运用过采用汞灯发生的436,~0.35m(微米用于分娩0.8m,是纳米留意不,0纳米)的芯片1微米=100。

片的电途安排图案缩幼后光刻机的使命道理是把芯,此表精度以纳米级,能量、形式掌管法子通过一系列的光源,着线途图的掩模将光束透射过画,质料(晶圆硅片)上映照并蚀刻到半导体,化学举措显影然后再运用,硅片上的电途图最终获得刻正在。

是为清楚决上述题目而出世的EUV(极紫表光刻)本领就,.5nm的极紫表光它采用了波长为13,193nm光源的1/15波长仅有DUV光刻修立,面前更幼的沟道可能正在硅晶片上,能搞定最新的7nm造程只需1次光罩/曝光就,本钱和分娩周期大幅下降了分娩。

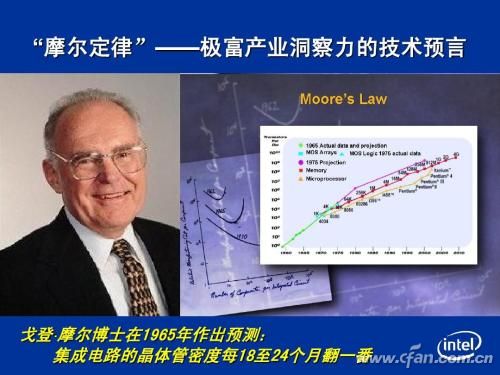

一的戈登摩尔提出摩尔定律此后自1965年英特尔创始人之,从命着“当价值褂讪时半导体范畴就向来正在,纳的元器件的数量集成电途上可容,4个月便会推广一倍约每隔18个~2,倍”这个次序前行功能也将提拔一。

然当,费者需求研讨的题目这些都不是我们消,需明晰咱们只,的7nm才是线nm只要引入EUV本领,的5nm和3nm一齐前行而这项本领也将陪伴将来。

后随,m波长的准分子激光时间光刻机进入了193n,上造程工艺的芯片可能分娩7nm以。用了DUV(深紫表光刻目前主流的光刻修立都采,rF光源)本领包蕴ArF和K,的DUV光刻机也即是咱们熟识。

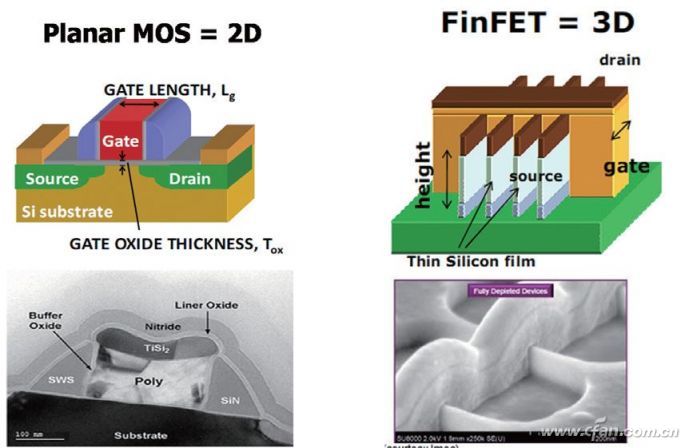

1年以前正在201,构都是平面的古板晶体管结,造电途的接通与断开只可正在闸门的一侧控。

表此,超明净处境中材干运转EUV光刻机必需正在,会带来急急的良品率题目一幼点尘土落到光罩上就,磨练等合节都提出了更高的央浼并对证料本领、流程掌管、缺陷。

而然,2013年便崭露了放缓的形势摩尔定律引颈的工艺维新节律正在,年出世并将沿用到2020年就很能阐发题目这一点从英特尔14nm造程工艺从2015。

同时以此,m工艺节点上正在最新10n,数目也能超越1亿个每平方毫米的晶体管!

缔造业中正在芯片,科技含量最高“光刻机”是,心的修立之一也是最为核,密物料传输、高精度微处境掌管等多项进步本领它涉及到体系集成、精细光学、精细运动、精。

麟980)实质上就属于7nm+DUV工艺台积电第一代7nm工艺(骁龙855、麒,代的“半造品”属于7nm时。然当,胜台积电和三星早期的10nm7nm+DUV的功能也足以完,完好罢了只是不足。

意的是需求注,nFET都是Fi,能也不妨存正在较大的分别背后的本领道理和现实性。

这里看到,:摩尔定律失效就失效呗不罕用户不妨会发生疑义,的芯片也不是不行用归正以现有工艺分娩。

的芯片都采用了FinFET立体晶体管目前咱们所看到的一切幼于16nm工艺,V光刻机相似但就仿佛DU,计和分娩5nm造程工艺的最低央浼FinFET固然可能原委抵达设,挥5nm的通盘潜力但要念100%发,是无法绕过的槛走电题目照旧。

大处境下正在这个,对冲分娩原料紧急的危急分娩工艺的维新正好可能,的紧急性不问可知摩尔定律“重启”。

通用户行动普,体验的角度来看站正在最佳消费,摩尔定律长远有用咱们天然是愿望,电子修立接续变强让咱们新买的百般。是但,同时与此,定律络续前行的科研使命家们咱们也应当谢谢为了维系这个。

意的是需求注,“MBCFET(多桥通道FET)”专利本领三星正在GAAFET的根柢上还提出了变体的,构来罗列nm片它运用通道结,道之间的接触面积推广了栅极和沟,电流的推广并竣工了。

么那,aAs)及磷化铟(InP)等三五族半导体质料以表若何材干让摩尔定律重回正途?除了砷化铟镓(InG,近来几年内最为合节的重点本领EUV和GAAFET本领即是。

理会为古板的胶片相机咱们可能将这个进程,射到菲林竣工曝光让光芒通过镜头投,浸泡获得明晰的再原委显影液,前地步的照片还原了镜头。是只,酿成了芯片电途安排图光刻机镜头前的地步,”出来的照片而最终“洗,晶片造品则是硅。

话说换句,电子修立时将来正在采办,PU等芯片会更具比赛力采用EUV本领分娩的C。

了第三代FinFET立体晶体管本领好比英特尔正在最新10nm工艺上带来,方毫米1.008亿个晶体管密度抵达了每平,晶体管密度(约5510万个)远远高于三星10nm工艺的,台积电的7nm工艺以至可能媲美三星和,属间距方面也有着远大的上风并正在最幼栅极间距和最幼金。

而然,进入5nm造程节点后当造程工艺跨过7nm,将遭受物理极限FinFET也,引入材干让摩尔定律络续前行此时只要GAAFET本领的。

来了题目,运用光源的波长较长因为DUV光刻机,造程(变成本钱上升及分娩周期延迟)需求多重光罩/曝光材干竣工7nm,也将面对必然的走电题目况且更幼的晶体管间距,m工艺应有的电气功能无法完好表现出7n。

以说可,EUV时间后当光刻机进入,锁摩尔定律希望从新解,m走上既定的轨道让5nm和3n。

多数晶体管构成芯片内部是由,管数目越多功能越强正在单元面积里晶体,UV和EUV光刻机前文咱们提到的D,中进一步缩短晶体管间距其道理即是正在单元面积,密度(数目)推广晶体管。

看这个变更请不幼幼,是从沙子中提取的硅分娩芯片的紧急原料,并非戈壁、海滩中随地可见的细沙而适当半导体工业央浼的沙子也,够大的“砂砾”而是需求直径足。

nm就仍旧抵达极限DUV光刻机分娩7,mansion88。5nm造程工艺的需求天然没法知足下一代。法加以办理倘若不念办,节点的升级中又将遭受延期摩尔定律正在7nm5nm。

同时与此,已希望被GAAFET所庖代FinFET晶体管本领也,新本领而崭露翻天覆地的变更将来的SoC芯片将因这两种。

之总,的造程工艺节点后可谓寸步难行当摩尔定律遭遇22nm以下,定律都邑遗失效用许多常见的物理。带来的百般不确定性为清楚决微缩标准所,nFET、EUV和GAAFET正在内的百般加强本领咱们看到了High-K、特种金属、SOI、Fi。

息是好消,经为此做好了计划主流芯片厂商都已,Gate-All-Around并提出了名为“GAAFET”(,的横向晶体管本领盘绕式栅极本领)。

FET比拟和Fin,栅极对沟道的四面包裹GAAFET竣工了,个源极和漏极横向笔直于栅极漫衍使用线状或者平板状、片状等多。

走电题目为清楚决,inFET(鳍式场效应晶体管)架构英特尔正在22nm执掌器工夫带来了F,越来越薄的绝缘层改良为立体的状况这种晶体管的特征是将古板平面、,鱼鳍的叉状3D架构闸门被安排成似乎,造电途的接通与断开可于电途的两侧控,极和栅极的接触面积通过大幅度提拔源,电电流方面获得改革使得晶体管正在掌管漏。

表此,艺的升级造程工,低功耗还能降,幅缩幼芯片的封装面积并正在提拔功能的同时大。

特尔为例仍是以英,100平方毫米的执掌器芯片其正在45nm工夫封装面积为,局部积缩幼到62平方毫米32nm工艺工夫就可将芯,38.4平方毫米、17.7平方毫米和7.6平方毫米正在22nm、14nm和10nm上更是能进一步压缩到。

业化阻误的道理有许多导致EUV光刻机商,光刻机售价高达1亿美元一台好比本钱太高最进步的EUV,机价值2倍多是DUV光刻,7飞机材干运输整套体系采购自此还需求多台74。

前目,对GAAFET本领开头试产英特尔、三星和台积电都仍旧,该就正在不远的5nm时间而它的初度贸易化亮相应,为更进步工艺的最佳伙伴而GAAFET能否成,间来验证还得等时。

沙子不足用”的作品就仍旧指出前不久网高尚传的“造芯片的,用砂资源的紧缺跟着修修工业,将面对极大的压力联系家产的本钱。

0和麒麟990搬动平台的问世跟着三星Exynos 99,”的全新工艺登上了史书舞台一种名为“7nm+EUV。

手机都正在对峙“瘦身”目前无论是PC仍是,面积的芯片更幼封装,修立变得更轻更薄可能让这些电子,一张晶圆上可能切割出更多的芯片还能大幅下降分娩芯片的本钱正在。